EDA tool optimises cell libraries for processor cores in SoCs

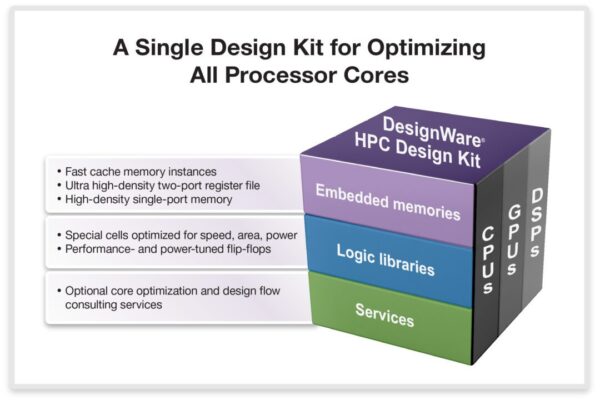

Synopsys has announced an extension to its DesignWare Duet Embedded Memory and Logic Library IP portfolio specifically designed to enable the optimised implementation of a broad range of processor cores. The new DesignWare HPC (High Performance Core) Design Kit contains a suite of high speed and high density memory instances and standard cell libraries that allow system on chip (SoC) designers to optimise their on chip CPU, GPU and DSP IP cores for maximum speed, smallest area or lowest power – or to achieve an optimum balance of the three for their specific application. Synopsys developed in collaboration with partners including Imagination Technologies, CEVA and VeriSilicon.

The tool operates in conjunction with the synthesis stage of a design flow (in a flow where the synthesis is aware of floorplanning issues), and is in part empirical; based on studies of “what works best” when implementing logic structures typical of processor cores, it selects and lays down specific standard cell variants when it recognises certain features of processor logic, improving speed, power and silicon area. It includes around 125 new cells and memory elements. Initially focused on TSMC’s 28-nm HPM process, Synopsys says it will produce variants for other processes at that node, including low-power versions; 16-nm fin-FET processes are a further possible target, and the company “may” look back at 40-nm processes if demand exists. The optimisation package uses standard “Liberty” syntax.

According to Mark Dunn, executive vice-president of IMGworks SoC Design at Imagination Technologies, “Our most recent project was building a PowerVR Series6 GPU core using cells and memories from Synopsys’ HPC Design Kit. We achieved an overall reduction of 25% in dynamic power as well as a 10% area savings, with some blocks achieving a 14% area improvement. We also created a tuned design flow that has delivered a 30% improvement in implementation turnaround time.”

The DesignWare Duet Package of Embedded Memories and Logic Libraries contains all the physical IP elements needed to implement a complete SoC including standard cells, SRAM compilers, register files, ROMs, datapath libraries and Power Optimisation Kits (POKs). Options for overdrive/low- voltage process, voltage and temperature (PVT) corners, multi-channel cells, and memory built-in self-test (BIST) and repair are also available. The DesignWare HPC Design Kit adds performance, power and area optimised standard cells and memory instances tuned for the special speed and density requirements of advanced CPU, GPU and DSP cores.

The HPC Design Kit contains fast cache memory instances and performance tuned flip-flops that enable speed improvement of up to 10% over the standard Duet package. To minimise dynamic and leakage power as well as die area, the new kit provides area optimised and multi-bit flip-flops and an ultra-high density two-port SRAM, delivering demonstrated reductions in area and power of up to 25% while maintaining processor performance. Synopsys adds that the package pays particular attention to clock tree synthesis, as that is where a great deal of power is consumed in advanced SoC designs.

Optimised design flow scripts and expert core optimisation consulting, including FastOpt implementation services, are also available from Synopsys to help design teams achieve their processor and SoC design goals in the shortest possible time.

Synopsys, www.synopsys.com/hpc-ip

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News