IBM slashes next-gen power

Dynamic — and interconnect-boosting harnesses what is ordinarily an adversary to speed — capacitive coupling — to momentarily boost supply voltage during operations for up to three-times faster access to SRAM with a 200 picosecond clock pulse width resulting in only a minuscule increase in power, according to IBM scientist Rajiv Joshi and colleagues at the Watson Research Center in Yorktown, Heights, New York.

"We are offering excellent solutions, which will be needed for future generations. In our work we have shown an excellent scalability through novel circuit techniques and predictive analytics," Joshi told EE Times. "We will attempt to make these circuits even more efficient/cost effective exploiting the future technology beyond 14nm."

All of Joshi’s group’s experiments, so far, have been on silicon-on-insulator (SOI) substrates at the 14nm node using immersion lithography. IBM has mastered this in the lab, achieving the lowest reported operating voltage (0.3) for a FinFET, even in the presence of process variability which gets worse when scaling beyond 14nm to 10-and-7nm.

"Process variability, which we call process, voltage and temperature related, is a greater challenge to get to 7-nanometer," Joshi said.

IBM Research (Yorktown Heights, N.Y.) has discovered a way to cut supply voltage to just 0.2 volts, clearing the way to 10-to-7 nanometer at lower power than Intel, according to scientist Rajiv Joshi (pictured above). Source: IBM.

IBM, however, believes that investments in its own unique design methodology tools—including predictive analytics and Technology CAD (TCAD)—has and will continue to allow it to overcome the obstacles to its "boosting" technology beyond the 14nm node, by anticipating problems and solving them before they even crop-up on test chips in the lab.

"Our super-fast predictive failure analytic techniques are state of the art, novel and proven, which will help take us to the 7nm regime by predicting design failures," Joshi said.

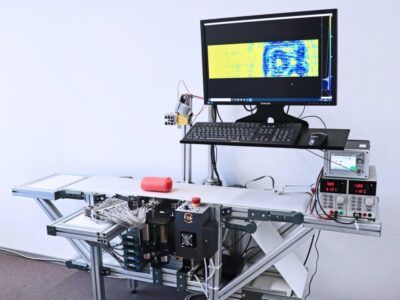

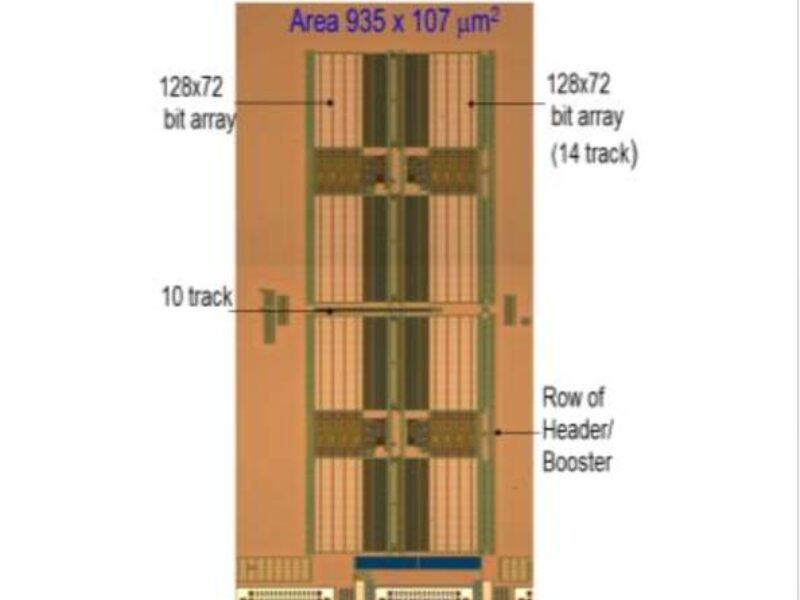

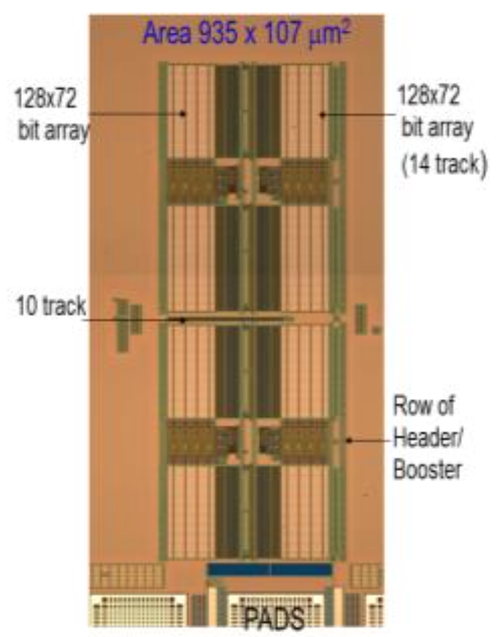

The boosting technique is combined with a simultaneous negative boost to bit-lines to improve yield. The only reported downside to IBM’s boosting technology is that it consumes about four percent of an SRAM die albeit in a header outside the array itself (see photo).

Test static random access memory (SRAM) fabricated with 14 nanometer finned field effect transistors (FinFETs) proves header boosters, according to IBM, can get to 0.2 volts to drastically cut power while improving performance. (Source: IBM)

"We have compared the area of this boost technique along with drivers to a commonly used header device alone and found there is a small percentage of area increase,” Joshi said. “ If we compare boost circuits without the header device then the area penalty would increase even more. In real life there is no free lunch. However, this will still get us the desired result that we want and the area penalty is outside of the macro without degrading the array efficiency much."

Other researchers have tried dual power supplies, charge pumping or other active circuitry techniques to give temporary boost low supply voltages, but according to IBM their efforts have consumed too much power and area, plus were specific to the circuit type, whereas IBM’s technique works on any FinFET—logic or memory.

Get all the details in the paper "14nm FinFET Based Supply Voltage Boosting Techniques for Extreme Low Vmin Operation" published in the conference proceedings of the IEEE’s 2015 Symposium on VLSI Technology (Kyoto, Japan).

About the author:

R. Colin Johnson is Advanced Technology Editor at EE Times

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News