RISC-V processor Mr Wolf arrives to solve problems

PULP is a European parallel ultra-low power processor initiative based on the RISC-V open-source processor instruction set.

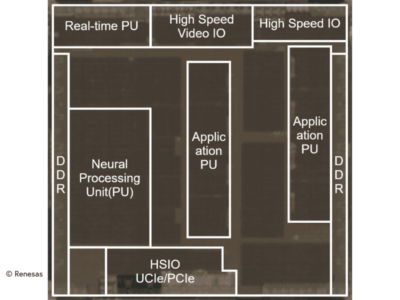

Mr Wolf is a cluster based processor that features eight 32-bit RI5CY cores implementing the RISC-V ISA, according to Frank Kagan Gurkaynak, director of the microelectronics design center at ETH Zürich, who announced Mr. Wolf’s arrival by way of an article on LinkedIn. Besides supporting standard (I)nteger, (C)ompressed, (M)ultiplication and 32-bit (F)loating-point extensions of RISC-V, it also provides our custom e(X)tensions for DSP operations. This processor core is written in System Verilog and is openly available from Github under the SolderPad License.

The processor can shut down its cluster completely and continue to run on a ninth core, which is a zero-riscy core, a smaller and leaner 32-bit RISC-V core developed for control applications, Gurkaynak said. Like Mr. Wolf, zero-riscy is free to download.

The Swiss and Italian researchers have received 200 Mr. Wolf chips manufactured in TSMC’s 40LP manufacturing process that were run through the Europractice multiproject wafer (MPW) scheme.

“We actually plan to release the entire Mr. Wolf code later this year. Of course, various NDAs prohibit us from releasing technology specific data, our releases contain only System Verilog code, testbenches and associated files for verification,” Gurkaynak.

Related links and articles:

News articles:

Swiss open-source processor core ready for IoT

Startup plans 4k RISC-V cores on 7nm chip

SiFive launches Linux-ready RISC-V quad-core processor

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News