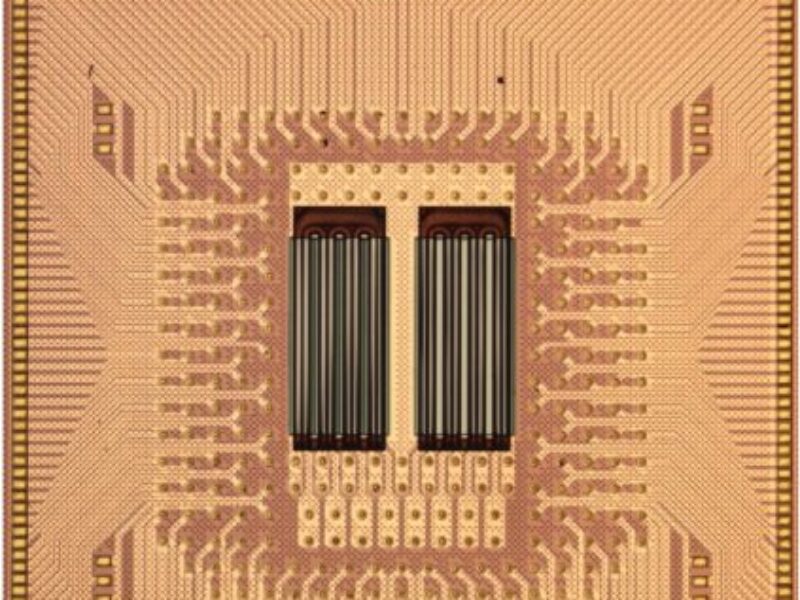

By locating the magnetic inductors on the bottom of a 3-D chip stack, the demonstration showed how a voltage regulator’s ordinarily bulky discrete components can be integrated into an otherwise CMOS design flow. Although the through-silicon-vias (TSVs) and other voltage regulator components were absent, the proof-of-concept demonstration shows how voltage regulators on silicon interposers can be integrated into future 3-D chip stacks.

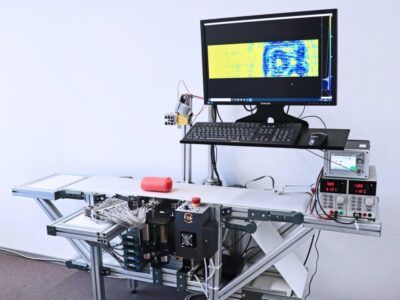

"What we have done at this point, is integrate the power inductors on a silicon interposer in what we call a 2.5-D stack—not true 3-D since we don’t yet have TSVs," said Ken Shepard, a professor at Columbia University. "The next step, which we are already fabbing, is a full 3-D stack where the silicon interposers contains not only the power inductors, but also the power train—the transistors that switch those power inductors—enabling power to flow from the package up through the interposer, where it is converted down in voltage then sent up through TSVs to power the CMOS chip itself on top."

Today voltage regulators are located on separate chips combined with discrete components that must feed printed-circuit board (PCB) traces connected to chip pins, requiring large currents to be pushed through extensive power distribution networks, presenting problems with both loss and power supply integrity. However, by switching the industry to voltage regulators located at the bottom on 3-D chip stacks, future self-regulating 3-D CMOS chip stacks will allow these high current levels at low supply voltages to be generated right at the load, improving overall energy efficiency by up to 20 percent, according to SRC.

Future voltage regulators on silicon interposers also promise to provide all the various voltages required by modern processors and memory chips, as well as manage smart energy conservation techniques, such as scaling the voltage and frequency to match the current workload. The researchers claim that integrated voltage regulation (IVR) will be able to respond to the energy needs of future CMOS chips in nanoseconds, compared to microseconds with off-chip voltage regulators, enhancing the ability to balance workloads on multi-core processors with its switched-inductor voltage converters.

The Columbia University effort, in partnership with IBM where the fabrication is being performed, claims that IVR could shave up to $270 million off the electricity bills of datacenters nationwide.

All the details are available in an ISSCC paper entitled: "A 2.5D Integrated Voltage Regulator Using Coupled Magnetic Core Inductors on Silicon Interposer Delivering 10.8A/mm2.

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News