Discovering Deadlocks in Memory Controller IP

By

U-Blox Oski

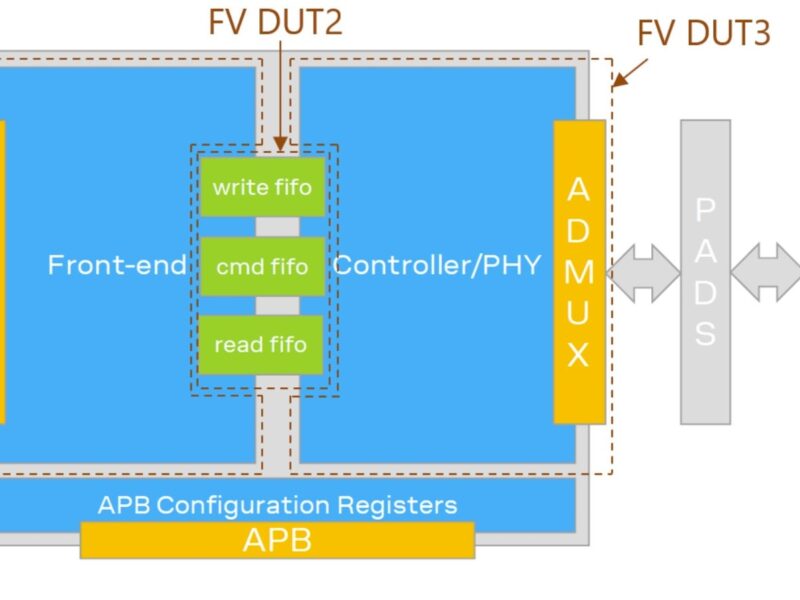

Formal deadlock verification is an effective and pragmatic method for discovering deadlocks in complex SoC IP blocks. For the MC design, the authors used Level 4 formal techniques to find deadlock bugs that were undetected through many millions of cycles of dynamic testing.

Disclaimer: by clicking on this button, you accept that your data might be communicated to this company. If you do not want us to communicate your data, please update your details on your profile

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

White Papers