16nm FPGAs pack more memory and hard IP, save power

The devices not only leverage the performance/watt boost from TSMC’s 16FF+ FinFET 3D transistors, they also includes a new interconnect optimization technology dubbed SmartConnect and claimed to provide an additional 20-30% performance, area, and power advantages, together with larger memory blocks to create high capacity on-chip memory for a variety of use cases.

The so-called UltraRAM blocks pack several hundreds of megabits up to 432Mbits and complement the previous generation BlockRAM (in the tens of megabits) for longer buffering such as deep packet and video buffering.

The UltraScale+ family including the company’s Kintex UltraScale+ FPGA, Virtex UltraScale+ FPGA and Zynq UltraScale+, is said to deliver value far beyond a traditional process node migration – providing 2 to 5X greater system level performance/watt over 28nm devices.

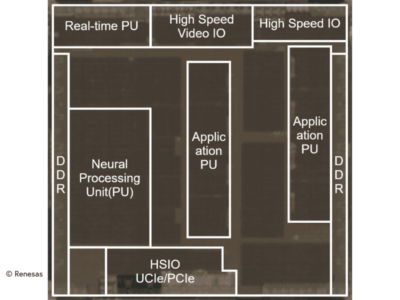

The MPSoC technology stands for heterogeneous multi-processing, examplified by the Zynq UltraScale+ family which integrates several hardened IP blocks to deliver approximately 5X system level performance/watt relative to previous alternatives. At the center of the processing-subsystem is the 64-bit quad-core ARM Cortex-A53 processor, capable of hardware virtualization, asymmetric processing, and full ARM TrustZone support.

The processing sub-system also includes a dual-core ARM Cortex-R5 real-time processor for deterministic operation, ensuring responsiveness, high throughput, and low latency for the highest levels of safety and reliability.

A separate security unit enables military-class security solutions such as secure boot, key and vault management, and anti-tamper capabilities—standard requirements for machine-to-machine communication and industrial IoT applications.

For complete graphics acceleration and video compression/decompression, the new device incorporates an ARM Mali-400MP dedicated graphics processor as well as a H.265 video codec unit, combined with support for Displayport, MIPI and HDMI.

Finally, dedicated platform and power management unit (PMU) has been added that supports system monitoring, system management and dynamic power gating of each of the processing engines.

First tape out and early access release of the design tools are scheduled for the second calendar quarter of 2015. First ship is scheduled for the fourth calendar quarter of 2015.

Visit Xilinx at www.xilinx.com

Related articles:

Xilinx lays grounds for 16nm FPGAs with new architecture

Turning FPGAs into programmers’ best friends

Xilinx’ SDNet: where software defined networks truly begin

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News