Marvell’s 2nm silicon demonstrates stacking for datacenters

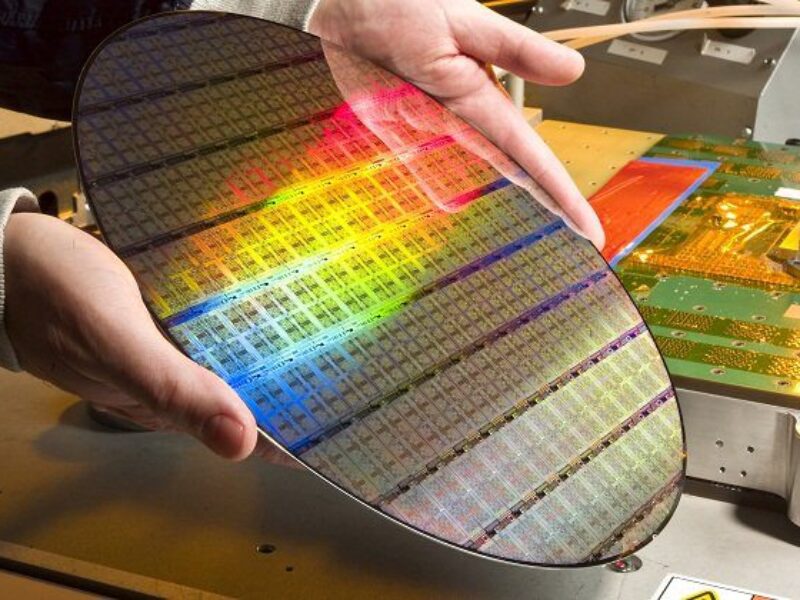

Marvell Technology Inc. (Santa Clara, Calif.) has demonstrated 2nm silicon IP for use in chips for AI and cloud infrastructure. It supports bidirectional die-to-die interconnect for vertical stacking.

Marvell has used TSMC’s 2nm manufacturing process and the working silicon is part of Marvell’s platform for custom processors and switches.

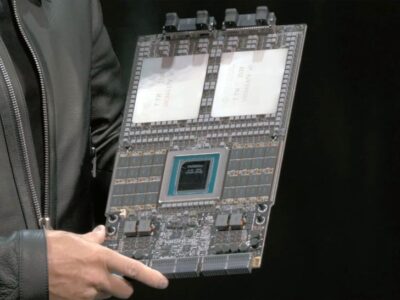

The device demonstrated allows 3D stacking of chips with simultaneously operating bi-directional I/O achieving speeds up to 6.4 Gbits/second. Shifting to a bi-directional I/O gives designers the ability to increase bandwidth or reduce the number of physical connections by a factor of two.

The advent of chiplet based design has been, in part, a response to advanced chips exceed the size of the reticle, or photomask, for outlining transistor patterns onto silicon. The ability to stack chips vertically – as is already done in DRAM and NAND flash memories, will alleviate the pressure to fragment designs into chiplets, Marvell said.

The Marvell platform strategy requires a broad portfolio of semiconductor IP. This includes:

- electrical and optical serializer/deserializers (SerDes)

- die-to-die interconnects for 2D and 3D devices

- advanced packaging technologies

- silicon photonics

- custom high-bandwidth memory (HBM) compute architecture,

- on-chip SRAM

- system-on-chip (SoC) fabrics

- compute fabric interfaces such as PCIe Gen 7

Such a family of IP enables the assembly of custom AI accelerators, CPUs, optical DSPs, high-performance switches and other technologies.

Marvell stated that it announced a similar 3nm platform in 2022 with first silicon appearing in 2023 and that is now has multiple standard and custom chips now shipping and in development.

The company did not indicate when it expects to release 2nm chips but extrapolation from the previous information would put the arrival in 2026.

“Our longstanding collaboration with TSMC plays a pivotal role in helping Marvell develop complex silicon solutions with industry-leading performance, transistor density and efficiency,” said Sandeep Bharathi, chief development officer at Marvell, in a statement.

Related links and articles:

News articles:

Marvell partners with Micron, Samsung, SK Hynix on custom HBM

Marvell founders back data centre RISC-V chiplet startup

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News