Next generation Virtusoso AI design tool targets SiP, 5G

Cadence Design Systems has launched the latest version of its Virtuoso RF and mixed signal design tools, adding generative AI technology and integration with microwave design tools.

Virtuoso Studio is aimed at mixed signal, analog, RF, photonic and heterogeneous 3D-IC for system in package (SiP) designs, integrating with its cloud platform and cloud-based solvers and analysis tools. Opening up cloud processing and the use of AI can make the tools three times faster, says Cadence.

The launch is supported by Analog Devices, TSMC, Renesas and Mediatek.

Virtuoso Studio is newly integrated with the AWR Microwave Office, Pegasus Design Rule Check (DRC) Solution and Layout Versus Schematic (LVS) tool alongside the the Spectre Simulation Platform, Allegro PCB Design and Pegasus Verification System.

These provide mmWave design and interactive signoff quality analysis during layout creation. Designers can also access the Spectre Simulation Platform, including the Spectre X Simulator and Spectre FX Simulator, through Virtuoso Studio, which allows for the analysis of the largest analog and mixed-signal designs.

Cadence has added generative AI for design migration which is supported by the foundries to simplify the move from older process technologies to ones with more capacity. Tools within the Virtuoso ADE Suite quickly re-centre and validate designs after the migration and take existing IP and transform it for their next-generation designs.

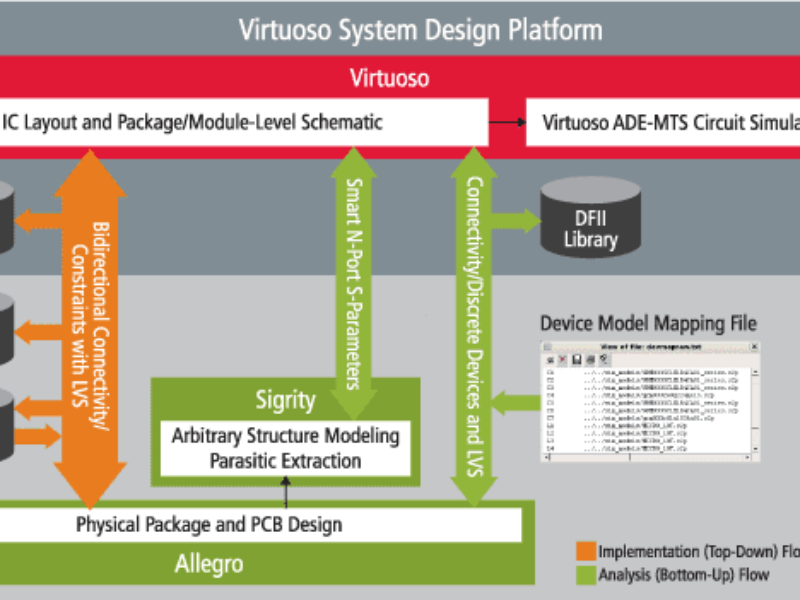

Combining the Virtuoso Schematic Editor and the Virtuoso Analog Design Environment provides a single platform for IC-and package/system-level design capture, analysis, and verification.

The Virtuoso System Design Platform also provides an automated bidirectional interface with the Cadence SiP-level implementation environment and Clarity 3d Solver. This has an automatically generated “system-aware” schematic where the results can be easily used to create a testbench for final circuit-level simulation. The Virtuoso System Design Platform automates the flow, eliminating the highly manual and error-prone process of integrating system-level layout parasitic models back into the IC designer’s flow.

System in a package (SiP) is one of the most common methods of integrating mixed technologies into a single design. This approach requires seamless integration between the IC and package substrate design teams and an integrated tool flow. The Virtuoso System Design Platform addresses these challenges with a cross-platform approach that streamlines and automates the design of a package/module featuring off-chip devices and multiple ICs based on differing process design kits (PDKs).

A new Design Space Optimization feature lets designers use AI algorithms to navigate competing specifications and aid in design centreing, particularly after the process migration of a design. Customers can experience faster interactive editing in both the layout and schematic tools, thanks to optimized code and algorithms, while multi-threading accelerates rendering, connectivity extraction and design rule checks in parallel.

The Cadence Spectre FMC Analysis is integrated into Virtuoso Studio and provides a complete machine learning (ML)-based Monte Carlo variation solution to deliver a 3-to-6-sigma yield with orders of magnitude speedup over brute force Monte Carlo analysis.

“Co-design of IC and package is critical for complex system-level product development, and ADI has closely worked with Cadence on the development of Virtuoso Studio to help meet the needs of our next-generation system design platform,” said Syam Veluri, senior director, Engineering Enablement, Analog Devices.

“At MediaTek, we push the boundaries of chip design by using the latest process technologies. The new device routing technology within Virtuoso Studio, when applied to cutting-edge manufacturing processes, provides us the next level of automation with excellent results and faster time to market,” said Ching San Wu, corporate vice president at MediaTek.

“Cadence and Renesas have worked closely together on analog design automation for over 20 years and continue to work toward achieving both improved design efficiency and design quality. With the release of the Virtuoso Studio platform, we look forward to improving design productivity by using the more automated environment with the new process migration flow and AI-based functions,” said Nobuhiko Goto, director, Design Automation Department, Shared R&D EDA Division at Renesas.

“TSMC has partnered with Cadence on the Virtuoso Custom Design Platform for over three decades. With the introduction of Virtuoso Studio, we look forward to continuing our collaboration on the forefront of tool development and next-generation design enablement for our customers on the world’s most advanced process technologies,” said Dan Kochpatcharin, head of the Design Infrastructure Management Division at TSMC.

www.cadence.com/go/VirtuosoStudio

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News