RISC-V AI chip runs on solar power

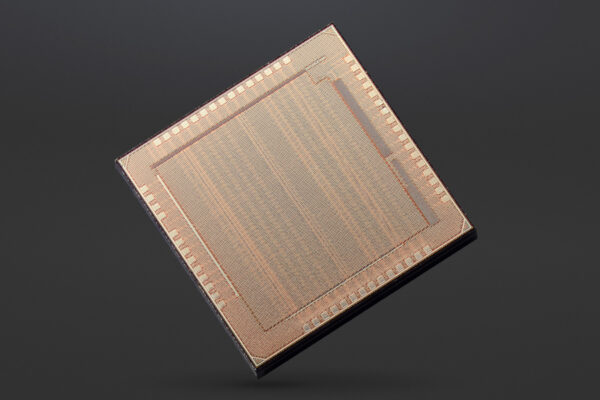

Engineers at CSEM in Switzerland have developed a low power RISC-V system on chip capable of carrying out AI operations using a small solar power or a tiny battery.

The 22nm chip dynamically trades image analysis depth, frames-per-second (FPS), accuracy, and power consumption to implement complete end-to-end edge processing, enabling always-on within the 1mW power budget of a 55mm diameter indoor solar panel such as those from Epishine in Sweden.

Machine learning frameworks can consume significant amounts of power. Chip developers such as Blaize have reduced the power consumption of AI processors for edge processing by focussing on specific AI frameworks such as imaging.

Instead the design couples a 32bit RISC-V processor developed at CSEM with two tightly coupled machine-learning accelerators: one for face detection, for example, and one for classification.

The first is a binary decision tree (BDT) engine that can perform simple tasks but cannot carry out recognition operations. The measurement results show the SoC operating in multiple sub-mW application scenarios using an in-house 320×320 pixel image sensor. The face detection BDT achieves 98 percent accuracy at twice the energy efficiency over other systems.

“When our system is used in facial recognition applications, for example, the first accelerator will answer preliminary questions like: Are there people in the images? And if so, are their faces visible?”, said Stéphane Emery, head of system-on-chip research at CSEM. “If our system is used in voice recognition, the first accelerator will determine whether noise is present and if that noise corresponds to human voices. But it can’t make out specific voices or words – that’s where the second accelerator comes in.”

The second accelerator is a convolutional neural network (CNN) engine that can perform ML frameworks. This two-tiered data processing approach drastically reduces the system’s power requirement, since most of the time only the first accelerator is running.

This achieves 0.32-1.07 TOPS/W efficiency including memory power. The RISC-V controller achieves 3.2 CoreMark/MHz at 2.23µW/MHz.

As part of their research, the engineers enhanced the performance of the accelerators themselves, making them adaptable to any application where time-based signal and image processing is needed.

“Our system works in basically the same way regardless of the application,” said Emery. “We just have to reconfigure the various layers of our CNN engine.”

The low power consumption enables an edge AI node to run for over a year on a coin cell battery.

Related articles

- UK startup develops high efficiency solar cells for the IoT

- Samsung moves to solar powered TV remote controls

- Solar energy harvester IC that operates with indoor lighting

- Blaize details architecture of GSP edge AI chip

Other articles on eeNews Power

- Skeleton adds €29m for fast charging battery production

- FPGA targets USB interfaces with low power ASSP

- Renesas, Maxpower team for motor control

- UK industry calls for more battery gigafactories

- Backside power opens up new realms in chip design

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News