5nm ASIC designs start

ASIC house Alchip Technologies in Taiwan is accepting 5nm design and expects first test chips in December.

Marvell is offering its IP through its ASIC business to support 5nm designs, and seven direct customers for TSMC’s 5nm process have been identified. NXP is also working with TSMC on an automotive qualfied version.

Alchip’s 5nm design flow is aimed at minimizing design turnaround time with a focus on reducing power and size rather than increasing performance with an initial focus on chips for data centres. This avoids problems with timing closure and will help to reduce costs: CHIP DESIGN IS ONE THIRD MORE COSTLY THAN AT 7nm.

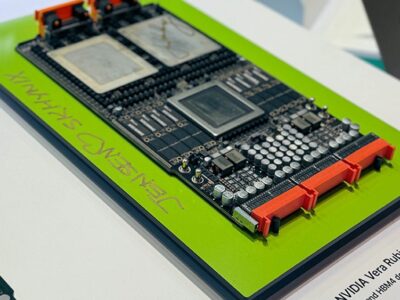

To help this, the physical design capabilities include a chiplet technology platform, high performance computing IP portfolio, IP sub-system integration services and 2.5D heterogeneous packaging capabilities. These packaging technologies include multi-chip modules (MCM) and two technologies from foundry TSMC: Chip on Wafer substrate (CoWoS) and Integrated Fanout on Substrate (InFO_os). These are critical for the 5nm production, says Alchip, which is a TSMC accredited supplier.

The company expects that 5nm demand will come initially from high-performance cloud computing applications. It says it expects the 5nm chips will be half the size of 7nm devices and use only 36 percent of the power for a similar speed (up three percent).

Alchip 5nm designs will draw upon a high-performance computing IP portfolio that includes DDR5, GDDR6, HBM2E and HBM3 memory interfaces as well as D2D, PCIe5 and 112G SERDES IP for data interfaces. Alchip’s in-house IP sub-system integration services cover PCIe5, DDR5, HBM2E/3, and 112G PAM4 serdes.

Package design covers thermal simulation that provides plug-and-play post silicon solutions to reduce substrate layers and the resulting cost. The result is more accurate power and thermal estimation flows for high power designs that have avoided post-silicon surprises.

“We’re rolling out our 5nm capabilities now to meet hyper-scalers’ demand that is being driven by the work-from-home, online-everything and business continuity surge trends that are driving significant data traffic and demand-pull for compute workloads,” said Johnny Shen, Alchip President and CEO. “We’ve made a commitment to the market that we would meet the demands of advanced technology head-on and today’s announcement substantiates that commitment.”

For 7nm designs, the company expects to have nine chip tape outs by the end of 2020, having completed three designs in May alone.

Related 5nm articles

Other articles on eeNews Europe

- II-VI buys Swedish SiC wafer maker Ascatron

- 3D printing quantum dot nanopixel displays

- 3D rolled filter cuts chip footprint

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News