Hybrid co-verification platform offers automated FPGA partitioning software

New Products

|

By

eeNews Europe

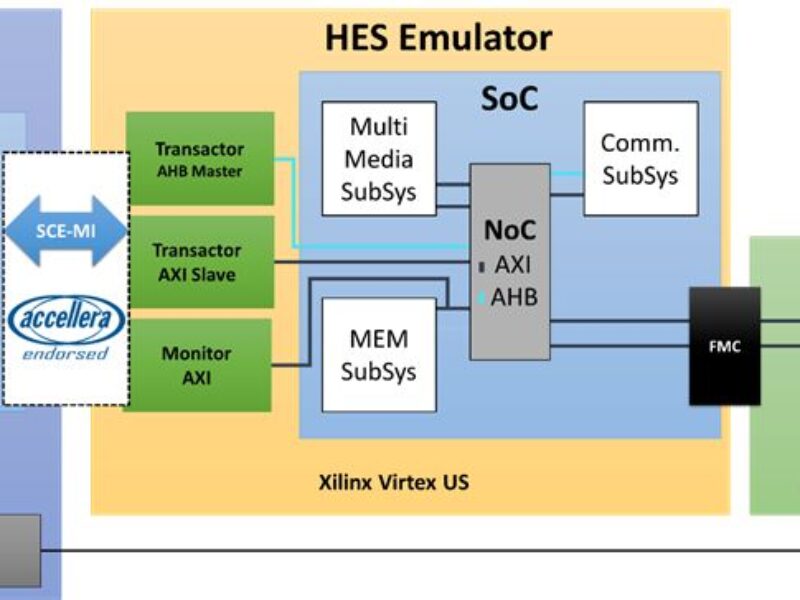

An FMC Host2Host bridge between the two Aldec products allows the TySOM board to share the ARM cores with the HES, meaning the software team members can prototype on fast clock-speed hardware and benefit from fast system boot-up (minutes instead of hours).

The company has also demonstrated automatic FPGA partitioning for its HES-DVM tool; the company’s fully automated and scalable hybrid verification environment for SoC and ASIC designs. Traditionally, and subject to design complexity and constraints, the manual partitioning of multiple FPGAs used for prototyping can take days, or even weeks, whereas HES-DVM can perform the task in minutes.

Aldec- www.aldec.com

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News