Presto in exclusive Cadence deal

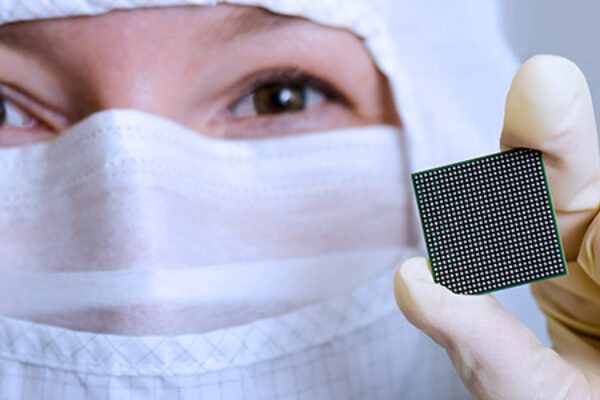

French test and ASIC design house Presto Engineering has signed a deal with Cadence Design Systems for a full tool flow that will include exclusive elements for system in package (SiP) development.

“By exclusivity we mean that Presto Engineering is investing into common development of new features and/or will be an alpha and beta tester of the new modules of the Cadence Suite,” said Cedric Mayor, vice president global strategy and corporate development at Presto.

“Indeed, Presto is designing very specific and sometimes quite unique heterogenous package SIP that have extraordinary form factor or bill of material,” he said. “It means that sometimes Presto will encounter tool limitations and will help Cadence in specifying new modules to overcome these limitations. Obviously such background IP and co-validation is intrinsically relying on exclusivity.”

Presto, based in Meyreuil, France, is working with Cadence on semiconductor SIP package design technology for the automotive and Industrial IoT markets. Presto is adopting the Cadence Allegro X Package Designer Plus, Clarity 3D Solver, Sigrity XtractIM technology and Celsius Thermal Solver, on an exclusive basis in order to design IC packaging for its automotive and IoT customers.

Presto will also provide Cadence with input on software features, functions and workflows specific to Cadence’s end customer and market needs.

Last year Presto bought the Delta Microelectronics ASIC design business from Force Technologies, adding sites in Hørsholm, Denmark and Hengoed, UK.

“Developing today’s complex semiconductor packages, such as heterogeneous SiPs with 3D chip stacks and high-speed data transfer packages, requires a high level of collaboration between IC designers and package engineers,” said KT Moore, vice president, product management in the Custom IC & PCB Group at Cadence. “With no two package designs being alike, collaborating with Presto allows us to capture insights on state-of-the-art package design trends as well as design team collaboration and workflow productivity.”

SiP and 3D packages often need multiple design spins in order to optimize the bill of materials and design tolerances, as well as to achieve full control of the chip’s performance reproducibility. ““In our efforts to date, we have already seen a 50 percent faster turnaround time due to a reduction in design iterations enabled by Cadence technologies,” said Mayor at Presto.

www.presto-eng.com; cadence.com

Related articles

- Turning ordinary testers into extra-ordinary instruments

- Presto offers CMOS image sensor testing service

- Europe’s largest independent semiconductor testing facility

- RS Components adds SnapEDA component library to DesignSpark

Other articles on eeNews Europe

- Vodafone launches commercial 5G standalone IoT pilots

- Micron, Mouser sued in Germany

- Intel to offer RISC-V core in 7nm foundry

- Chip shortage hits payment cards

- Cutting noise with a lightweight metamaterial sound screen

- ST, Tower to share 300mm Agrate fab

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News