SDK and neural network IP for low-power FPGA-based smart vision

Microchip’s VectorBlox Accelerator SDK is designed to enable developers to code in C/C++ and program power-efficient neural networks without prior FPGA design experience.

The highly flexible tool kit can execute models in TensorFlow and the open neural network exchange (ONNX) format which offers the widest framework interoperability. ONNX supports many frameworks such as Caffe2, MXNet, PyTorch, and MATLAB. Unlike alternative FPGA solutions, Microchip’s VectorBlox Accelerator SDK is supported on Linux and Windows operating systems. It also includes a bit accurate simulator which provides the user the opportunity to validate the accuracy of the hardware while in the software environment. The neural network IP included with the kit also supports the ability to load different network models at run time.

“In order for software developers to benefit from the power efficiencies of FPGAs, we need to remove the impediment of them having to learn new FPGA architectures and proprietary tool flows, while giving them the flexibility to port multi-framework and multi-network solutions,” said Bruce Weyer, vice president of the Field Programmable Gate Array business unit at Microchip.

“Microchip’s VectorBlox Accelerator SDK and neural network IP core will give both software and hardware developers a way to implement an extremely flexible overlay convolutional neural network architecture on PolarFire FPGAs, from which they can then more easily construct and implement their AI-enabled edge systems that have best-in-class form factors, thermals and power characteristics.”

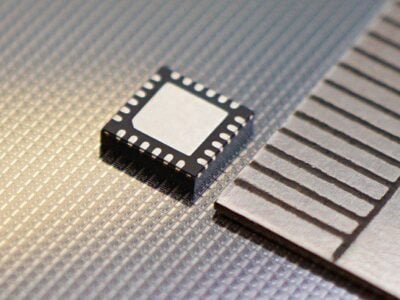

For inferencing at the edge, PolarFire FPGAs deliver up to 50 percent lower total power than competing devices, while also offering 25 percent higher-capacity math blocks that can deliver up to 1.5 tera operations per second (TOPS), says the company. By using FPGAs, developers also have greater opportunities for customization and differentiation through the devices’ inherent upgradability and ability to integrate functions on a single chip. The PolarFire FPGA neural network IP is available in a range of sizes to match the performance, power, and package size tradeoffs for the application, enabling customers to implement their solutions in package sizes as small as 11x11mm.

Microchip Technology – www.microchip.com

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News