Astonishing and shocking drop in first silicon success

Siemens EDA has highlighted shocking drop in the success of first silicon across the semiconductor industry.

First silicon success is declining, down from 24% in 2022 and 32% in 2020 to just 14% in 2024, says Abhi Kolpekwar, VP and general manager of Design Verification Technology at Siemens EDA, which is part of Siemens Digital Industries Software.

“This is an astonishing and shocking drop both in ASIC as well as FPGA, “he said. “This is a very big problem that goes back to the complexity of designs that people tape out today.”

The company has developed a suite of interlocked tools for verification of designs using AI agents to try to tackle the issue.

“The second issue is in timing constraints. 75% of projects are behind schedule. Then the skilled workforce is only able to meet 20% of the demand so 80% of the requirements are going unfilled at the moment.”

“My business is all about helping people functionally verify their designs before tape out, identifying any bugs in a design as quickly and as early as possible. The more the bugs stay in the system the costlier they become so the game plan is to catch as many as possible while they are cheap so that people don’t need to respin their designs.”

- Siemens EDA boosts power verification in mixed signal tool

- Questa IQ drives AI and data analytics into verification

“Just producing faster simulators is not enough. We need faster engines, faster engineers by automating tasks and analyses, and fewer workloads. All of this provides a 5x improvement in total end user productivity,” said Kolpekwar.

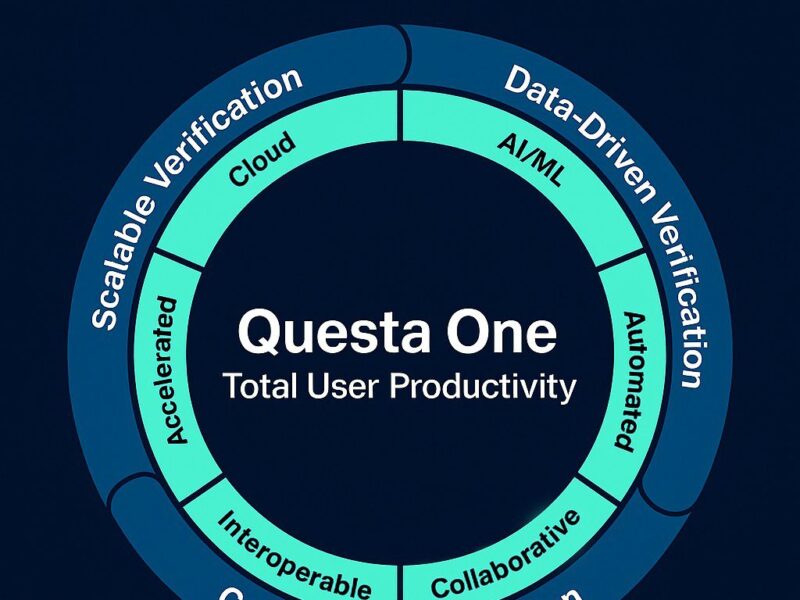

Questa One has three elements, with a new simulation engine, verification tools and verification IP, all using generative AI and AI agents. The tools are being used by ARM, Mediatek, Rambus and Microsoft.

For example a Smart Creation tool take a design requirement and translates that into a design requirement for formal verification using Generative AI. A Smart Regression tool identifies failure patterns and uses predictive AI for fast debugging of problems.

“Rather than running thousands of regression tests, you only have to run a few hundred optimised tests for any design changes. There is also the ability to predict the test cases that are likely to fail and these are ordered first so that if the regression fails you don’t have to run the rest of the tests,” said Kolpekwar. “This is how we use AI to reduce the workload.”

A Smart Engine has access to all the design databases and testbenches to accelerate the computation of the data, accelerating the simulation, while a smart debug tool uses AI to identify the failure and provide the root cause analysis to specific code.

A new simulation engine has been developed that supports parallel simulation with automatic partitioning, functional safety simulation and static and dynamic power analysis.

The AI is trained on standard documentation in Siemens EDA before it is shipped to customers and the model will train as it stays on the system using a local training model with retrieval augmented generation (RAG).

This simplifies the verification tool chain.

“You can use generative AI code generation for test benches, and also for running formal checkers, but that’s not enough,” said Kolpekwar. “You can pick up sections from design requirements documents, and generate the assertions directly from the documents.”

Another part of the QuestaOne verification tool chain is stimulus free verification (SFV) for static and formal verification to find bugs without the need for testbenches.

“The idea of SFV combines static and formal analysis using GenAI, LLMs, predictive and analytic AI,” he said, “Rather than firing up a linter where the user asks questions, we apply the linter, find the violations and auto fix then we run an RTL to TRL equivalency check.”

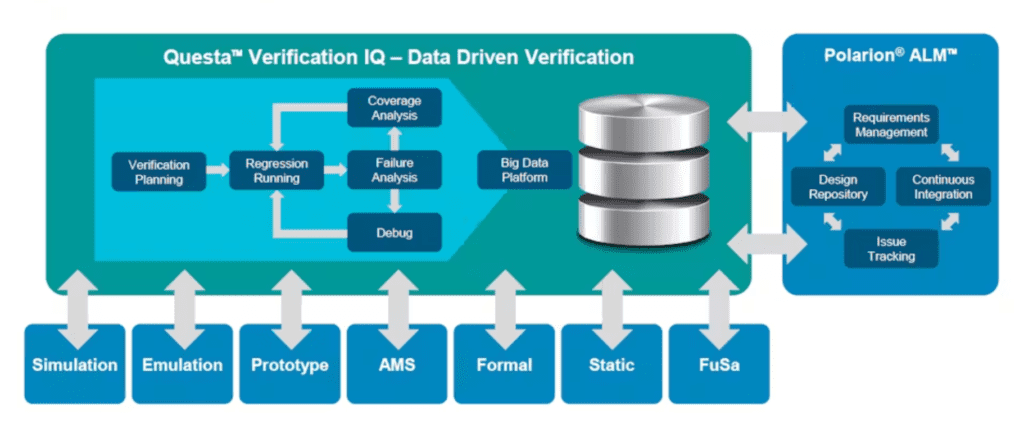

The Verification IQ tool uses analytic AI and generative AI to automate tasks and automate workloads. This comes from the acquisition of Avery Design Systems in 2023.

“We are building on that baseline protocol technology to bring the infrastructure of test cases and AI applications through the ecosystem of verification IP. Since we acquired them we have created an ecosystem of verification IP with simulatable and emulatable IP on QEMU software emulation and Veloce hardware emulation.”

There are initial users across a wide range of applications, from automotive and AI accelerator chips to memory devices and aerospace designs.

“We have customers who have given feedback on speeding up complex designs, automating tasks to do the tasks faster and helps the design verification managers save resources,” said Kolpekwar.

“The Questa One Smart Verification Solution has improved our verification productivity across traditional on-premises and cloud deployments,” said Karima Dridi, Head of Productivity Engineering at ARM. “As an early adopter of running large EDA workloads using the high-performance Questa One Sim advanced functional simulator, we’ve observed improvements in performance, cost-efficiency, and reduction in regression time on the latest AArch64 architecture.”

“As an early influencer on Siemens Questa One Smart Verification Solution, MediaTek has already been able to increase our engineers’ productivity across the entire verification process utilizing both formal verification and simulation technologies,” said Chienlin Huang, senior technical manager of Connectivity Technology Department, MediaTek. “Questa One Property Assist utilizes generative AI to save us weeks of engineering time, and Questa One Regression Navigator predicts which simulation tests are most likely to fail, runs them first, and saves days of regression and debugging time.”

“Questa One DFT (QDX) simulation utilizes advanced DFT-centric simulation capabilities to deliver faster performance than existing simulation solutions, slashing our verification time from weeks to days,” said Claudia Muia-Tartevet, Director of DFT at Microsoft. “In addition to these impressive speed ups, on Microsoft’s Azure Cobalt 100 platform, QDX delivers up to 20 percent further performance jump unlocking even greater efficiency for our EDA workloads.”

“Siemens’ Questa One smart verification has improved and streamlined our verification process, enabling us to address new-era data centre workloads like generative AI with state-of-the-art silicon IP solutions for PCIe, CXL and HBM interfaces,” said Susheel Tadikonda, vice president of Engineering, Silicon IP at Rambus. “Leveraging the complete Questa One solution, including simulation, static and formal analysis, and verification IP technologies, brings increased confidence to our customers through comprehensive verification of IP solutions for their SoC and chiplet designs.”

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News