Chasing integrated quantum chips with FD-SOI

Cette publication existe aussi en Français

Cette publication existe aussi en Français

A quantum startup out of CEA-Leti in France is aiming to use existing silicon manufacturing with FD SOI to build large scale superconducting integrated quantum chips and computer systems.

Siquance was set up with the research from Leti by Maud Vinet (above) and two fellow researchers to tap into the silicon ecosystem around Grenoble, particularly the expertise in fully depleted silicon on insulator (FD-SOI), and the move to the next generation 10nm and 7nm geometries with the pilot line being built.

So the startup is looking in detail at the architecture required for integrated chips with control electronics and arrays of spin qubits on the same device that can be used in a supercooled cryostat.

“Six months ago we launched a startup to build a quantum computer using silicon based on 15 years of our research,” she said. “As a startup we now have 10 employees and we are building a team with expertise in physics and technology.”

“There is a lot of at stake as if we can make quantum computing happen it will have an impact on all industries that use high performance computing (HPC) today. But this will happen only if we can make a lot of high quality qubits.”

Spin qubits

So far there have been prototype technologies that have not had many qubits and not of high quality, she says. This is what is driving the push to error correction, to create a logical qubit out of thousands of physical devices.

- Intel shows mass produced 12qbit CMOS quantum chip

- Intel boosts EUV quantum dot yields

- IBM to develop 100k-qubit quantum-centric supercomputer

- Leti details move to 10nm, 7nm FD-SOI process in Europe

“To be useful we need to be above 100,000 qubits and the path to that is not known today,” she said. “This is what Siquance is promising is to find the path to and silicon will help pave the way to large scale quantum computing.”

“Silicon allows the design of good qubits, around 100nm2, that are high quality with millisecond coherence and microsecond speeds,” she said. “This is hard to do. Transistors and qubits are very different and there is definitely a rift between transistors and qubits. The way transistors were optimised was to deliver large currents at room temperature while for qubits have a single charge and are very sensitive to their environment.”

“In the physics labs there are many systems to implement silicon spin qubits. After the first demonstration of a couple of qubits how do we repeat this with high performance qubits everywhere? By using FD-SOI we can bridge the gap between transistors and qubits where we can design arrays of qubits with control electronics on the same substrate with packaging to fit into the cryostat. The advantage is the qubits are in a 1cm2 chip and as we upgrade we can take the card out of the cryostat and put in a new one.”

“FD-SOI has a big advantage by biasing the back gate we can move the charges away form the interfaces and this makes the charges less sensitive to noise. Using this we have decreased the charge noise by a factor of ten. We developed the proof of concept in 2016, and have over 40 patents licensed to the startup.

Since then the quality of the spin qubits has been improved using both holes and electrons, and the advantage is that the higher coherence time allows the qubits to couple with a photonic qubit over a distance of 2 to 3mm, rather than having to have a separation of a few nanometres.

Integrated quantum chips

“The main challenge is to control the thermal dissipation from the control electronics and FD-SOI is again very interesting for this,” said Vinet.

“We know the industry needs statistical data at low temperature which is the missing part for the full chain and we are working on the control signals and qubit control protocols to increase fidelity to 99.99%. That leads to record hole coherence time.”

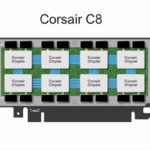

Working with STMicroelectronics and Global Foundries, the startup plans to have a system in package (SiP) in 2025, combining an array of qubits with the controller logic. This controller will be integrated with a 2D array of qubits on a single chip by 2027. This will lead to multicore quantum chips with 2D arrays of qubits that can run on the premises of customers, says Vinet.

- £6.5m project to develop cryogenic CMOS IP for quantum computing

- SureCore expands into control logic for quantum computing

The energy consumption is also key as the quantum computer will operate at a few millikelvins.

“We already pay attention to the energy consumption and by increasing the quality of the qubits we can reduce the energy as you need less control electronics. There is a tradeoff and it is something we are looking at very carefully,” she said.

The next move is to evaluate the building blocks for the chips and the architecture. “It’s very interesting to have the analogue amplification with the transimpedance amplifier (TIA) close to the qubits. Then we are measuring building blocks, memories, comms, to see how much electronics we will embed close to the qubits,” she said.

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News