Streaming Scan Network cuts test cost for large system-on-chip designs

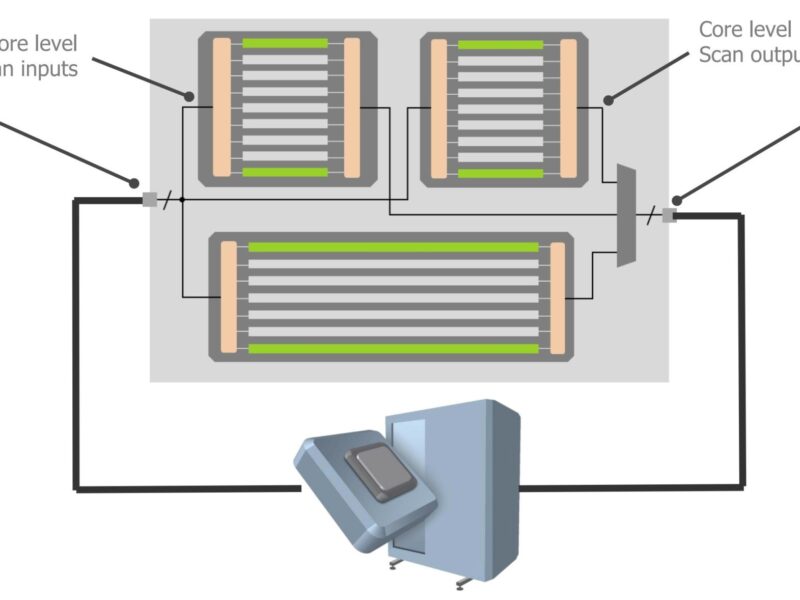

Mentor, part of Siemens, has developed a bus-based scan data distribution architecture that enables simultaneous testing of any number of cores. This helps shorten test time by enabling high-speed data distribution, efficiently handling imbalances between cores and supporting testing of any number of identical cores in a large system-on-chip design with a constant cost. It also provides a plug-and-play interface in each core that simplifies scan timing closure and is well-suited for abutted tiles.

The software includes embedded infrastructure and automation that decouples core-level DFT requirements from the chip-level test delivery resources. This enables a no-compromise, bottom-up DFT flow that can dramatically simplify DFT planning and implementation, while reducing test time by a factor of four. Mentor developed the technology in collaboration with multiple leading semiconductor manufacturers and is part of the reference flow for Samsung Foundry.

Growing demand for next-generation integrated circuits (ICs) that deliver the extreme performance required for fast-evolving applications such as artificial intelligence and autonomous driving has resulted in an unprecedented increase in the size of IC designs, which today can integrate many billions of transistors. Larger IC design sizes and associated complexity translate to a dramatic rise in the time and cost required to test these massive IC designs, as well as the engineering effort needed to plan for and deploy design-for-test (DFT) structures and functionalities across each design.

The Tessent Streaming Scan Network software is part of the TestKompress software and has full support for tiled designs and optimization for identical cores, so it suitable for increasingly large emerging compute architectures.

“The dramatic spike in IC test complexity due to increasing design sizes, advanced technology nodes, and use-model requirements presents significant challenges for IC design organizations,” said Brady Benware, vice president and general manager of Tessent Silicon Lifecycle Solutions for Mentor, a Siemens business. “With the Tessent Streaming Scan Network, our customers can be ready for the designs of tomorrow, while slashing test implementation effort and simultaneously optimizing manufacturing test cost today.”

The software consists of a series of host nodes in each design block that are networked together. Each host distributes data between the network and the test structures in the block. The software automates the implementation, pattern generation, and failure reverse mapping processes. DFT engineers can fully optimize DFT test resources for each block without concern for impacts to the rest of the design. This helps to dramatically reduce the implementation effort. Along with optimized handling of identical cores, elimination of waste in the test data, and time multiplexing, this solution enables substantial reductions in test data time and volume.

“With the support for Tessent Streaming Scan Network technology in Tessent TestKompress, we are able to offer our customers a scalable test access solution ideal for today’s and tomorrow’s advanced IC designs,” said Sangyun Kim, vice president of Design Technology Team at Samsung Electronics. “We have found that the Tessent Streaming Scan Network significantly reduces the effort needed to make complex designs highly testable.”

Tessent Streaming Scan Network is fully compatible with all other Tessent DFT products and can be combined with Tessent Diagnosis cell-aware and layout-aware diagnosis for a complete end-to-end defect detection and diagnosis solution. All Tessent DFT products are part of the Tessent Safe ecosystem and qualified for all ASIL ISO 26262 projects with a complete set of certified ISO 26262 documentation.

Mentor plans to show the Tessent Streaming Scan Network during the International Test Conference (ITC) this week

www.itctestweek.org; www.mentor.com/tessent

Related articles

- VERIFICATION REVIEW SERVICE SPEEDS UP CHIP DESIGNS

- DRIVING LEADING EDGE CHIP DESIGN FROM EUROPE

- ULTRASOC DEAL TRIGGERS SIEMENS TEST CHANGES

Other articles on eeNews Europe

- Five-minute breath test for Covid-19

- ST to make cartridges for Covid-19 tests

- Prototyping platform for silicon microfluidics

- Machine learning to remove space debris

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News