Astera Labs ramps production of PCIe 6 AI interconnect

Cette publication existe aussi en Français

Cette publication existe aussi en Français

Astera Labs is ramping production of its PCI Express 6 (PCIe) chips for a number of AI infrastructure platforms.

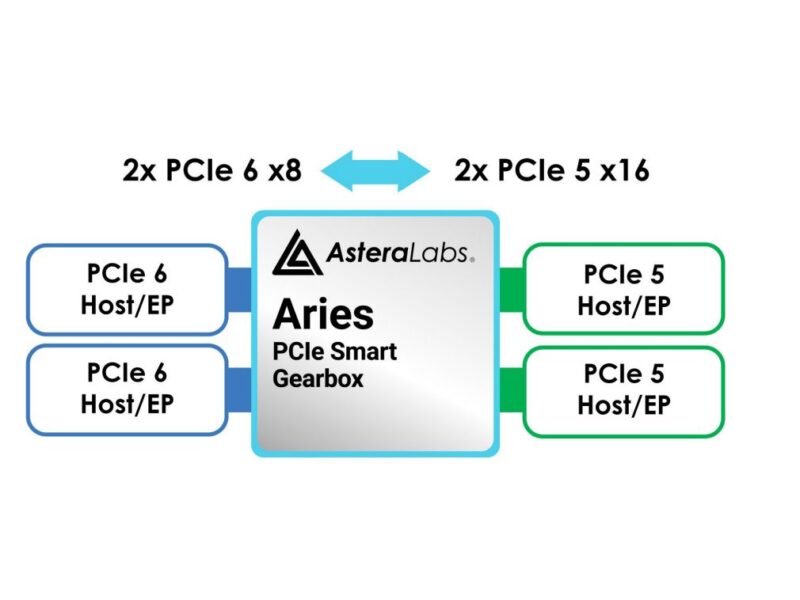

The company has added a gearbox that allows PCIe5 and 6 technologies to be combined, alongside the fabric switches, retimers, and active cable modules using the latest PCIe 6 standard.

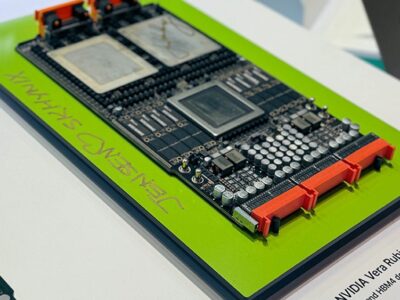

The transition to PCIe 6 is being driven by the demand for higher compute, memory, networking, and storage data throughput with hyperscalers rolling out systems later this year. The Aries 6 PCIe Smart Gearbox chip is sampling to allow processor and high speed memory with PCIe 6 interfaces to be added to existing systems.

Each port is independent and may operate at 64 GT/s, 32 GT/s, 16 GT/s, 8 GT/s, 5 GT/s, or 2.5 GT/s with a link width of x16, x8, x4, x2, or x1. This can add PCIe 5 channels alongside new PCIe 6 links and follows the first PCIe 6 interoperability demonstration back in March.

Customers for Astera include AMD, Samsung and Micron as well as server makers Inventec, Quanta, Wistron and WiWynn. The technology is also supported by Keysight Technologies and Teledyne Lecroy for test and validation.

“Our PCIe 6 solutions have successfully completed qualification with leading AI and cloud server customers, and we are ramping up to volume production in parallel with their next generation AI platform rollouts,” said Thad Omura, Chief Business Officer at Astera Labs. “By continuing to expand our PCIe connectivity portfolio with Scorpio Fabric Switches, Aries Retimers, Gearboxes, Smart Cable Modules, and PCIe over optics technology, we are providing our hyperscaler and datacentre partners all the necessary tools to accelerate the development and deployment of leading-edge AI platforms.”

“Inference has arrived and the next wave of AI infrastructure must pivot to address the deployment of AI agents and assistants. Inference generates more IOPS than any enterprise workload ever encountered. Micron and Astera Labs are leading the industry in delivering these IOPS through the early enablement of PCIe Gen6 high-performance SSDs. Micron’s commitment to technology innovation and broad ecosystem support has now resulted in verified interoperability with Astera Labs,” said Jeremy Werner, senior vice president and general manager, for the Core Data Center Business Unit, at Micron Technology.

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News