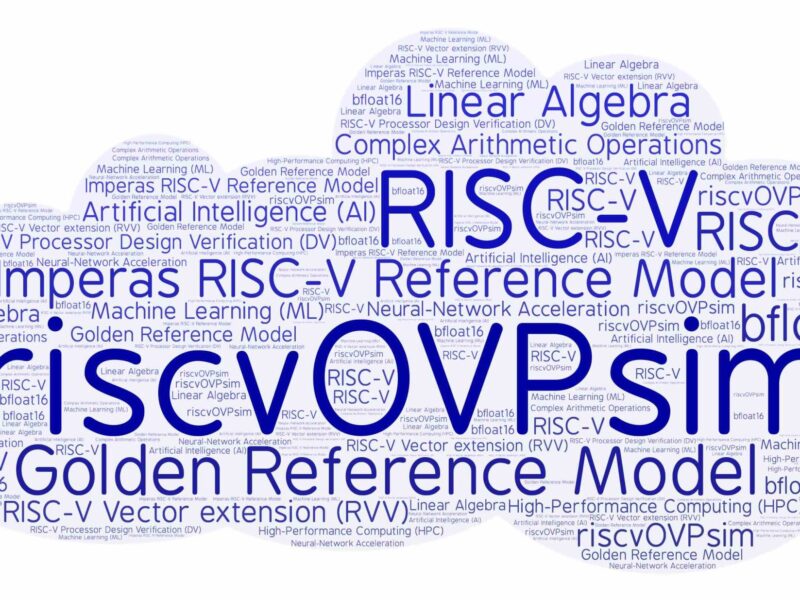

RISC-V reference simulator adds vector support

Imperas Software has updated and extended its reference simulator for RISC-V vector instructions and now supports coverage driven verification analysis.

The base version of riscvOVPsim is available for free from a new GitHub site, while an enhanced version including an extensive RISC-V vector test suite also freely available for commercial use from Open Virtual Platforms (see links below).

The upcoming ratification of the RISC-V Vector instruction extension offers system designers broad flexibility to configure vector engines to support complex arithmetic operations required for applications involving linear algebra, such High-Performance Computing and machine learning applications. With these latest enhancements to riscvOVPsim, software developers and system architects can start to explore RISC-V based solutions, while Design Verification (DV) Engineers can configure the models for test benches and test frameworks with coverage analysis.

The riscvOVPsim simulator includes an envelope model that supports all the RISC-V ratified specification options, which can be easily configured to match targeted processor features as a key step in setting up a verification test bench. riscvOVPsim has also been updated with coverage features that easily and efficiently support instruction functional coverage-based verification flows.

Imperas launched riscvOVPsim to support the RISC-V International compliance working group in 2018 and it has become widely adopted by both open source and commercial processor development teams looking for a dependable RISC-V reference model that can be easily configured and is the key reference within their compliance, directed and random test generation environments and frameworks.

The Imperas support for the RISC-V vector instruction extension also includes a new architectural validation test suite which features detailed instruction tests for a base vector engine configured as RV32GCV with elen:32, vlen:256, slen:256. The vector suite is built by the Imperas directed test generator and includes over 3 million instructions in 5-7,000 test files (depending on suite configuration), with full source, assertions, and reference signatures.

Next: RISC-V test coverage and links

The tests currently achieve over 85% instruction functional coverage which will approach 100% when the vector instruction extensions are ratified by RISC-V International. The test suite can be generated for any of the recent published draft specifications (including 0.8, 0.9, 1.0draft) and compliant vector engine configurations including enhanced options such as use of BFloat16 for floating point optimized for accelerating machine learning and near-sensor computing applications.

The simulator and test suites are freely available with many processor, behavioural, and virtual platform models, with various SystemVerilog examples and test benches for Hardware Design Verification and other community resources from Open Virtual Platforms.

“The RISC-V International working groups have made considerable progress in building a robust ecosystem of tools to help developers more easily test and verify RISC-V solutions,” said Mark Himelstein, CTO of RISC-V International. “We’re pleased to see Imperas’ contributions for this reference model and early RV32I test suite, which really underscore the importance of compliance suite adoption for the whole community.”

“The AndesCore NX27V processor was the first licensable RISC-V core to support the new RISC-V vector instruction extension,” said Charlie Hong-Men Su, CTO and Executive Vice President at Andes Technology Corp. “In addition to Andes’ own cycle accurate reference model, Andes has certified the Imperas RISC-V Vectors reference model for use with lead customers and partners with this exciting and powerful new era of compute technology.”

“An architectural validation suite is not a complete verification test plan for a RISC-V processor but shares many similar attributes and its adoption is always useful at any stage of a project,” said Bill McSpadden, Principal VLSI Verification Engineer at Seagate Technology, and co-chair of the RISC-V International’s Technical Committee task group for compliance. “Any test plan requires four items – a device to test, some tests, a reference to compare against and a test plan. An easy-to-configure reference model that supports coverage driven analysis, like Imperas’ riscvOVPsim, is central to any test plan.”

“RISC-V Vectors Extensions are not just a technical specification, they represent the framework to develop the next generation of compute engines for key markets with advanced requirements,” said Simon Davidmann, CEO at Imperas. “The dynamic multi-state operation of a vector processor is not just complex to design but is pushing the boundary of state-of-the-art design verification methodologies. Imperas simulation technology and reference models are now at the centre of the most advanced design verification teams adopting RISC-V.”

The free riscvOVPsim is now available on GitHub while the free enhanced riscvOVPsim including the vector test suite is now available on OVPworld.

Related articles

- RENESAS SIGNS DEAL WITH OPEN SOURCE ARM COMPETITOR

- AUTOMOTIVE GPU IS SAFETY CAPABLE WITH RISC-V CONTROLLER CORE

- FIRST FPGA DEVELOPMENT KIT FOR SIFIVE RISC-V ADDS EMBEDDED TRACE

Other articles on eeNews Europe

- Graphene electronics pilot line takes shape

- Opinion: Data centre AI drives $30bn AMD-Xilinx deal

- Multicore GPU aims at 3nm for data centre designs

- Ruthenium shows way to 2nm

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News