NVM memory chip breakthrough targets edge AI

As a world’s first, the researchers integrated multiple-bit non-volatile memory (NVM) Resistive RAM (RRAM) technology with silicon computing units, as well as new memory resiliency features said to provide 2.3-times the capacity of existing RRAM.

Target applications include energy-efficient, smart-sensor nodes to support artificial intelligence on the Internet of Things, or “edge AI”.

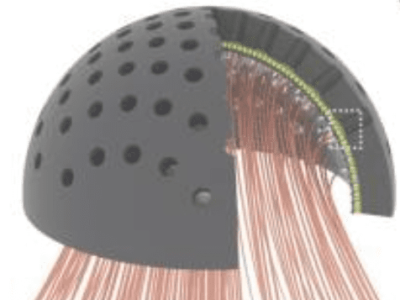

The proof-of-concept chip has been validated for a wide variety of applications such as machine learning, control and security. Designed by a Stanford team led by Professors Subhasish Mitra and H.-S. Philip Wong and realized in CEA-Leti’s cleanroom in Grenoble, France, the chip monolithically integrates two heterogeneous technologies: 18 kilobytes (KB) of on-chip RRAM on top of commercial 130nm silicon CMOS with a 16-bit general-purpose microcontroller core with 8KB of SRAM.

The proof-of-concept chip has been validated for a wide variety of applications such as machine learning, control and security. Designed by a Stanford team led by Professors Subhasish Mitra and H.-S. Philip Wong and realized in CEA-Leti’s cleanroom in Grenoble, France, the chip monolithically integrates two heterogeneous technologies: 18 kilobytes (KB) of on-chip RRAM on top of commercial 130nm silicon CMOS with a 16-bit general-purpose microcontroller core with 8KB of SRAM.

The new chip is reported to deliver 10-times better energy efficiency (at similar speed) versus standard embedded FLASH, thanks to its low operation energy, as well as ultra-fast and energy-efficient transitions from on mode to off mode and vice versa.

Non-volatility enables memories to retain data when power is off, an essential on-chip memory characteristic for edge nodes that must be able to turn themselves off. The 2.3 bits/cell RRAM enables higher memory density and was tested to yield better application results, such as a 2.3x increase in neural network inference accuracy, compared to a 1-bit/cell equivalent memory.

The CEA-Leti and Stanford team also created a new technique called ENDURER that overcomes the typical write failures of NVM technologies, giving the chip a 10-year functional lifetime when continuously running inference with the Modified National Institute of Standards and Technology (MNIST) database.

Mitra said the chip demonstrates several industry firsts for RRAM technology. These include new algorithms that achieve multiple bits-per-cell RRAM at the full memory level, new techniques that exploit RRAM features as well as application characteristics to demonstrate the effectiveness of multiple bits-per-cell RRAM at the computing system level, and new resilience techniques that achieve a useful lifetime for RRAM-based computing systems.

CEA-Leti – www.leti-cea.com

Stanford University – www.stanford.edu

Related articles:

CEA-Leti proves RRAM-based TCAMs viable for neuromorphic processors

University College London spins out ReRAM startup

Rambus, GigaDevice form ReRAM joint venture

Time is ripe for emerging non-volatile memory, says Yole

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News