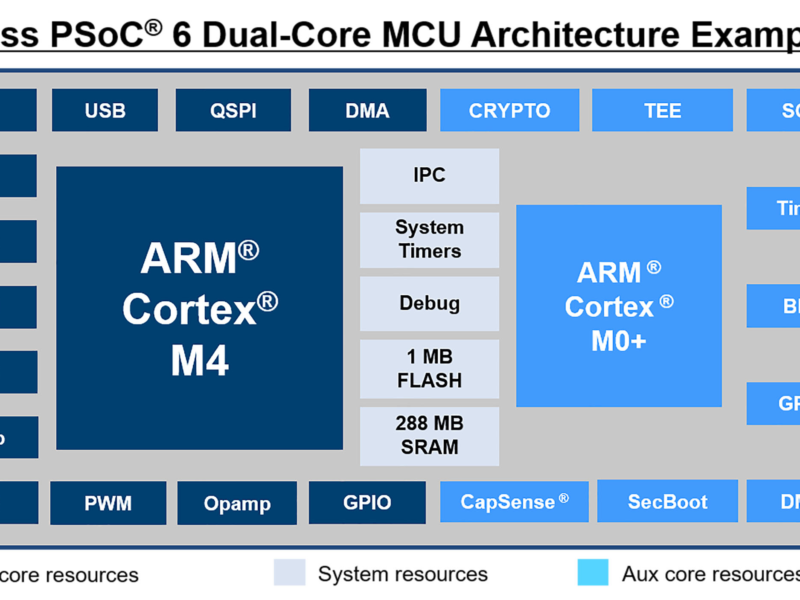

PSoC 6 is built around dual-core ARM Cortex-M4 and Cortex-M0+ at 40nm

The dual-core ARM Cortex-M4 and Cortex-M0+ architecture lets designers optimize for power and performance simultaneously. Cypress’ proprietary ultra-low-power 40-nm SONOS process technology enables the PSoC 6 MCU architecture to draw only 22µA/MHz and 15µA/MHz of active power on the ARM Cortex-M4 and Cortex-M0+ cores, respectively. With dynamic voltage and frequency scaling (DVFS), the PSoC 6 MCU architecture offers both performance- and power-critical processing capability. The dual-core architecture enables power-optimized system design where the auxiliary core can be used as an offload engine for power efficiency, allowing the main core to sleep. The PSoC 6 MCU architecture integrates a hardware-based Trusted Execution Environment (TEE) with secure boot capability and integrated secure data storage to protect firmware, applications and secure assets such as cryptographic keys.

The chip implements a broad set of industry-standard symmetric and asymmetric cryptographic algorithms in an integrated hardware coprocessor designed to offload compute-intensive tasks. The architecture supports multiple, simultaneous secure environments without the need for external memories or secure elements, and offers scalable secure memory for multiple, independent user-defined security policies. Software-defined peripherals can be used to create custom analog front-ends (AFEs) or digital interfaces for innovative system components, as well as supporting oflexible wireless connectivity options. The architecture is supported by Cypress’ PSoC Creator Integrated Design Environment (IDE) and the expansive ARM ecosystem.

Visit Cypress Semiconductor at www.cypress.com/PSoC6

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News