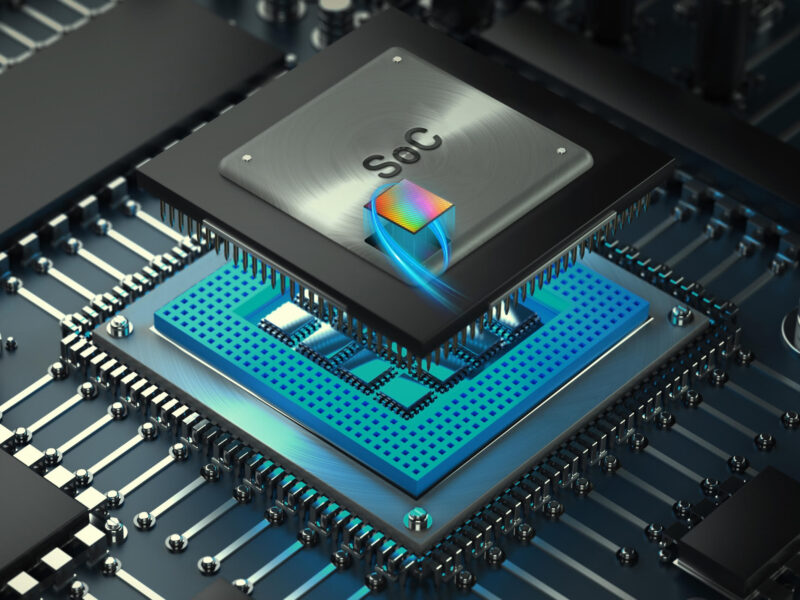

The following is a practical approach that helps designers in making a decision on whether an eFPGA is the right option for their next SoC.

Why consider an eFPGA

Designers encounter a broad variety of processing problems that are often ineffectively addressed by embedding a CPU or GPU in a SoC, and then relying on an external discrete FPGA for acceleration. Usually, the primary motivation for SoC design teams to explore embedding a programmable fabric is to add technology that can solve problems that are either intractable, or extremely costly to solve using traditional approaches.

Exploiting eFPGA IP, already proven in multiple ASIC designs, can allow SoC developers to add logic programmability to their solution resulting in a single device that can adapt to multiple applications. As well as the inherent system-level advantages of embedding a programmable hardware accelerator in an SoC, an eFPGA provides SoC designers with other advantages. For example, an eFPGA delivers a personalized combination of memory, LUT and DSP blocks matched to the end application. eFPGAs also offer improvements in bandwidth, signal delays, latency, power and importantly, cost. In addition to these advantages, board design becomes simpler, with power and cooling requirements are reduced. Finally, the system BoM cost is reduced too because the discrete FPGA, along with all of its supporting devices, such as level shifters and voltage regulators, are eliminated.

Once the decision to go down the eFPGA path has been made, the next question on a potential customer’s mind is along the lines of “never mind the data sheet, how do I assess Speedcore eFPGA IP’s ability to solve my problem?”

Phase zero, the first collaborative step

Typically, Achronix customers begin this process by getting a feel for Speedcore eFPGA IP via the design process. This process begins with developing example designs, prepared with many of the core functions customers require, using the Achronix ACE design tools. This step can help customers in familiarizing themselves with the Speedcore design flow and the resources available to support their own design efforts. This process helps to clarify customer design ideas for Speedcore IP in their potential ASIC and sets expectations for power composition and performance prior to having a final solution.

Phase zero quickly evolves into a highly collaborative engagement, which sees customers evaluating Speedcore eFPGAs through IP and design flow training, Q&A sessions, and application discussions. This interaction implicitly calls for the sharing of documentation, tools, expertise and detailed technical information. As a consequence, a mutual nondisclosure agreement (NDA) is required between Achronix and the customer to protect everyone’s intellectual property. Once the NDA is complete, Achronix will deliver login credentials to the evaluator(s) to allow them to download the ACE design tools and activate an evaluation license.

ACE includes an Achronix-optimized version of Synopsys Synplify Pro, as well as full support for Speedcore IP. To aid in the evaluation, ACE is shipped with two example Speedcore instances that can be targeted with sample designs. These two examples instances differ in size and resource counts (BRAM, LUTs, etc.) in order to allow the ASIC design team to compile their designs into a Speedcore eFPGA to gain a better insight into the design flow and performance.

Designers need a lot of feedback — ACE design tools produce multiple reports on performance, power consumption and resource utilization, as well as include tools for layout, place and route, bitstream generation, debug support, static timing analysis and both functional and timing-automated simulation. The Achronix applications team is available to provide training and support throughout the process.

Synthesis to metal stack

Using ACE software tools, customers have the ability to benchmark Speedcore IP by synthesizing RTL, targeting either of the two generic Speedcore sample instances. Often, this process is executed with the assistance of the Achronix applications team. During this phase, the evaluators typically collect resource utilization, as well as fMAX, and early power consumption profiles.

Once armed with data from this initial evaluation, customers are able to determine the appropriate mix of resources needed for their own unique Speedcore instance — an instance accommodating their exact requirements. Achronix responds with projected die size and aspect ratio of the IP, static power profile, configuration time, and the exact mix of programmable blocks. Variables that influence these early size assessments of a Speedcore instance include the design elements themselves, customer trade-offs between performance and power consumption, as well as the customer’s target process node and metal stack.

LUTs and LRAMs have evolved

There have always been hardware differences between various FPGA fabrics. The Speedcore eFPGA fabric is based on the 4-input LUT in contrast to the 6-input LUT architectures from other FPGA vendors. Using a 4-input LUT was a deliberate choice as empirical data indicates that 4-input LUTs provide the optimal performance with respect to silicon area for the vast majority of contemporary programmable logic applications.

One other significant difference is the distributed memory of the Speedcore fabric. Speedcore logic RAM (LRAM) blocks are 4,096-bit (configured as 128×32), making them larger than the distributed memory agreements for other competitors’ offerings and ideal for the midsize applications like buffering tasks. In fact, Speedcore LRAM has proven to be particularly well suited for a variety of networking and multimedia functions, including packet management and video processing. And by offering both block RAM (BRAMs) and industry-leading LRAMs, Speedcore memory blocks help designers choose the right memory configuration to optimize performance per square millimeter of silicon for their personalized Speedcore instance.

Primitive conversion and RTL

It is not unusual for eFPGA customers to begin with RTL that previously targeted a discrete FPGA, which is typically optimized for a particular FPGA vendor’s architecture. To re-target such code to the Speedcore architecture, an Achronix IP library is available to help with the conversion from Intel/Altera and Xilinx primitives to Achronix primitives. In addition, any RTL originally intended for standard-cell implementation will work for targeting Speedcore eFPGAs, but will benefit from efforts to optimize the code for the Speedcore architecture. Customers can review a published set of best practices for crafting code that makes more efficient use of Speedcore logic, memory and DSP resources.

Close collaboration throughout

The Achronix Applications team often becomes deeply involved with Speedcore customers. This involvement is a normal part of the collaborative evaluation effort between Achronix and ASIC teams and can be helpful for interpreting design results to drive further improvements in power consumption, compile times, configuration times and performance. Phase zero is just the beginning of a Speedcore engagement, which enables designers to fully explore the benefits of deploying an SoC with one or more customized Speedcore instances. Once phase zero is complete (which can be in as little as three weeks), all that is left to move the design forward is to complete the licensing agreement. Such an agreement (terms, conditions, duration) is comparable to licenses for embedded CPUs, standard-based circuit blocks, and most other embedded IP in the semiconductor industry. In short, determining whether a Speedcore eFPGA is the right move for your next SoC development is a straightforward evaluation process, aided closely by the Achronix team.

About the author:

Alok Sanghavi is Sr. Product Marketing Manager at Achronix Semiconductor Corporation – www.achronix.com

Related articles:

Achronix completes validation of 16nm embedded FPGA

Custom eFPGA blocks supercharge data acceleration systems

The case for integrating FPGA fabrics with CPU architectures

Quicklogic turns to licensing FPGA fabric

Sifive signs Flex Logix for low-cost FPGA fabric

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News