Samsung Foundry tapes out 3nm chips with Synopsys tools

Samsung Foundry has produced multiple successful test chip tapeouts on its SF3 3nm technology using digital and custom design tools and flows from Synopsys.

The SF3 process reduces power consumption by 50%, boosts performance by 30% and has 30% smaller area than Samsungs SF5E 5nm process.

Samsung uses Synopsys DSO.ai technology in its flow, tapping machine learning capabilities to massively scale the exploration of choices in chip design workflows and speed up the design flow.

In June Samsung announced internal first silicon for its 3nm nanosheet gate all around (GAA) Multi-Bridge-Channel FET (MBCFET) process. The second generation of this process has the same improvements as the SF3 process.

- Samsung Foundry tapes out 3nm GAA chip

- Tools enable 3nm designs on Samsung process

- Cadence, Samsung accelerate 3nm mixed-signal silicon

“Today’s demanding mobile, high-performance computing and AI applications require power and performance levels that stretch the limits of small geometries,” said Sangyun Kim, corporate vice president of the Foundry Design Technology Team at Samsung Electronics. “Our longstanding collaboration with Synopsys on EDA design flow certifications provides mutual customers with substantial power, performance and area advantages.”

“Synopsys’ strategic collaboration with Samsung Foundry has enabled us to remain in lockstep through every generation of their process technology advancements,” said Shankar Krishnamoorthy, GM of the EDA Group at Synopsys. “By providing leading EDA design flows certified on the most advanced Samsung 3nm technology, our mutual customers can maximize the capabilities of their advanced SoC designs and achieve a faster path to silicon success.”

www.synopsys.com/implementation-and-signoff/fusion-design-platform.html

Other articles on eeNews Europe

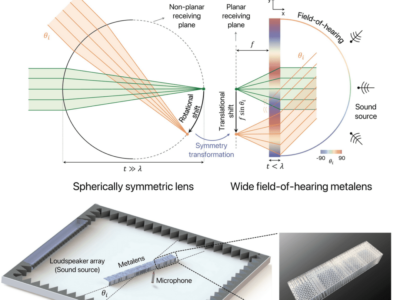

- Metasurface lidar reference design targets industrial, automotive

- Spain plans compound semiconductor photonics foundry

- OQC in first quantum computer co-location data centre deal

- Mobileye files for IPO, reveals data

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News